# **UART IP DESIGN USING VHDL**

# Dr. Prof. MEENA CHAVAN

# KUMAR ANANT, KISHTI JAIN, JYOTI SRIVASTAVA

BHARATI VIDYAPEETH DEEMED UNIVERSITY COLLEGE OF ENGINEERING, PUNE

DEPERTMENT-ELECTRONICS ENGINEERING

\_\_\_\_\_\*\*\*\_\_\_\_\_

**Abstract-**A Universal Asynchronous Receiver Transmitter (UART) is an integrated circuit that plays an important role in serial communication. The UART could also be a typical communication component that is provided by most of the offered microprocessors. Generally, the quantity of the UART throughout a silicon chip is restricted and not enough for automation applications. During this project, anintellectual property (IP) of UART style methodology by using VHISC Hardware Description Language (VHDL) is projected. It additionally provides a fast prototyping by synthesizing the required system with associate acceptable Electronic style Automation (EDA) tool.

Key Words: UART, VHDL, IP Properties, EDA Tool

#### 1.INTRODUCTION

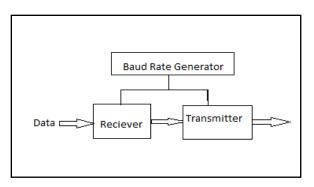

The UART contains a receiver (serial-to-parallel converter) and a transmitter (parallel-to-serial converter). It handles the conversion between serial and parallel knowledge. Serial communication reduces the distortion of a signal, so makes knowledge transfer between two systems separated in distance doable. Generally, the quantity of the UART throughout a silicon chip is restricted and not enough for automaton applications. A Intellectual property (IP) of UART style methodology by victimization VHISC Hardware Description Language (VHDL) is projected. The proposed UART IP consists of a baud generator, a receiver module, and a transmitter module. These modules are reusable and synthesizable.

#### **UART IP DESIGN**

The popular N-8-1 (No parity (N), eight (8) knowledge bits, and one (1) stop bit) format is enforced at intervals the projected UART information processing, however the parity setting, the quantity choice of data bits, and stop bits square measure user-enhancements. styles square measure delineated throughout a hardware description language like VHDL and square measure verified by simulation. because of these helpful options, the reconfigurable FPGA system as a result of the implementation platform of the mobile automation are usually used.

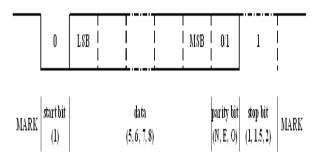

A UART frame consists of 1 begin bit, form of information bits, associate elective parity and 1, 1.5 or a pair of stop bits. The start bit goes low for 1 bit time, then form of information bits square measure transmitted, least vital bit initial, the quantity of data bits ranges is typically 5, 6, 7, or 8. When no data is being transmitted, a logic 1 should be placed at intervals the transmitted knowledge line. Fig. 1 shows the standard format for serial knowledge transmission. The quantity of data bits, the parity, and so the range of stop bits should be set a priori altogether communication partners. The look is minimalist, and no error checking logic is gifted by default.

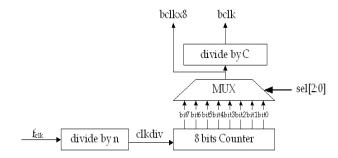

All of these options square measure to become userenhancement. Several UART perform multiple sample points to observe barely cell and select on a majority vote. This methodology affords a multiple of the Volume: 04 Issue: 09 | Sept-2020 ISSN: 2582-3930

frequency for single bit detection however provides immunity to shorts spike disturbances on the communication line. The UART information processing consists of a Baud Rate Generator (BRG), a receiver module, and a transmitter module.

Fig -1: Standard Serial Data Format

### **UART Transmission Protocol:**

It usually includes begin bit, data bit, parity bit, stop bit and idle state as shown is given to the UART for Asynchronous transmissions, barely referred to as the "Start Bit" is supplementary to the beginning of each word that is to be transmitted. The start Bit is utilized to alert the receiver that a word of data is about to be sent, and to force the clock in the receiver once the start Bit, the individual bits of the word of data square measure sent, with the Lowest Significant Bit (LSB) being sent initial into synchronization with the clock in the transmitter. When the complete data word has been sent, the transmitter could add a parity that the transmitter generates. The parity may even be utilized by the receiver to perform straightforward error checking. Then a minimum of 1 Stop Bit is sent by the transmitter. If incorrectly formatted knowledge is received, the UART could signal a framing error. If another computer memory unit is received before the previous one is scan, the UART can signal associate overrun error.

Fig 2.The baud rate generator design

#### **Transmitter Module:**

The transmitter module converts a parallel knowledge word into serial kind and appends the start, parity, and stop bits. The transmitter of UART consists of transmitted bit counter, an information register, a state machine and support logic. The transmitted bit counter has identical performance and implementation as that of the receiver, solely the signal name has modified slightly. The information register is associate 8 bits parallel-in-serial-out register. It's three management inputs: loadTSR, start and shiftTSR.An active high on the first signal loads the parallel data into the shift register. Also, high on the second signal transmits a start-bit (logic 0) for one bit time. A High on the last signal shifts the loaded knowledge out by one bit. Once the transmit operation is completed, the txd\_doneH are aiming to be a high signal for a system clock period. The information register is associate eight bits parallel-inserial-out register. It consists of three management inputs: loadTSR, start and shiftTSR.An active high on the first signal loads the parallel data into the shift register. Active High on the second signal transmits a start-bit (logic 0) for one bit time. High on the last signal shifts the loaded knowledge out by one bit. When the transmit operation is completed, the txd\_doneH square measure aiming to be a high signal for a system clock amount

Volume: 04 Issue: 09 | Sept-2020 ISSN: 2582-3930

Fig 3. UART Module

#### **Receiver Module:**

The task of the receiver is to receive a serial bit stream within the form; start bits, data, parity information, stop bits and store the contained data. To avoid setup and hold time problems and reading some bits at the incorrect time, we sampled serial data eight times during each bit time. That is, we sampled on the rising fringe of bclkx8. When rxd first goes to 0, we'll wait eight more bclkx8 periods, and that we should be near the center of the beginning bit. Then we'll wait eight more bclkx8 periods, which should take us near the center of the primary data bit. We continue reading once every eight bclkx8 clocks until we've read the stop bit.

## 3. CONCLUSIONS

UART architecture involves and plan to the serial communications. UART is appetent for providing an interface between RS232 line and a microcontroller or an IP core. The UART IP consists of a Baud Rate generator, a receiver module, and a transmitter module. It shows that the transmitter transmits the info and receiver receives the info with an equivalent baud. By this there's no loss of your time because it transmit and receive at an equivalent baud. These modules are reusable and synthesizable.

The main purpose of UART is to transmit and receive data. It's a Standard which will communicate peer to peer and even features a parity for error checking.

#### 4. FUTURE PLANS

Designs are described in a hardware description language like VHDL are verified by simulation. Due to these useful features, we can choose the reconfigurable FPGA system as the implementation platform of the mobile robot. The reusable UART IP design is composed of a baud rate generator, a receiver module and a transmitter module. These modules can be applied to various applications-

Mobile robots, including the distance information detector of the IR ranging system heading.

Output detector of the digital compass module.

Communications among soccer robots and a host computer.

#### **ACKNOWLEDGEMENT**

We would like to express our special thanks of gratitude to our Project Guide (Prof. Dr. Meena Chavan ) as well as our Head of The Department of Electronics Department, Bharati Vidyapeeth (Deemed University) College of Engineering, Pune (Prof. Dr. A.A. Shinde) who gave us the golden opportunity to do this wonderful project on the topic "UART IP DESIGN USING VHDL".

# REFERENCES

- [1] "VHDL For Design: A Guide to Using VHDLfor Hardware Design and modeling" By Stuart Sutherland, Simon Davidmann, Peter Flake.

- [2] VHDL 3.1a Language Reference Manual.

- [3] Kumari Amrita, Avantika Kumari "DESIGN AND VERIFICATION OF UART USINGVHDL" 28th -29th January 2018.

- [4] FANG Yi-yuan ,CHEN Xue-jun "Design and Simulation of UART SerialCommunication Module Based on VHDL.